http

hbase

客快物流大数据项目

数学

armv8

Debezium报错处理系列

便签

iVX

图像超分辨率

产品经理常犯的错误

web前端期末大作业

下载视频方法

PromQL

Material Design

firefox

网页作业

股票交易

Cadence Allegro

linux安装qt

颜宁

数字IC设计

2024/4/11 17:29:21【数字IC/FPGA】Verilog中的force和release

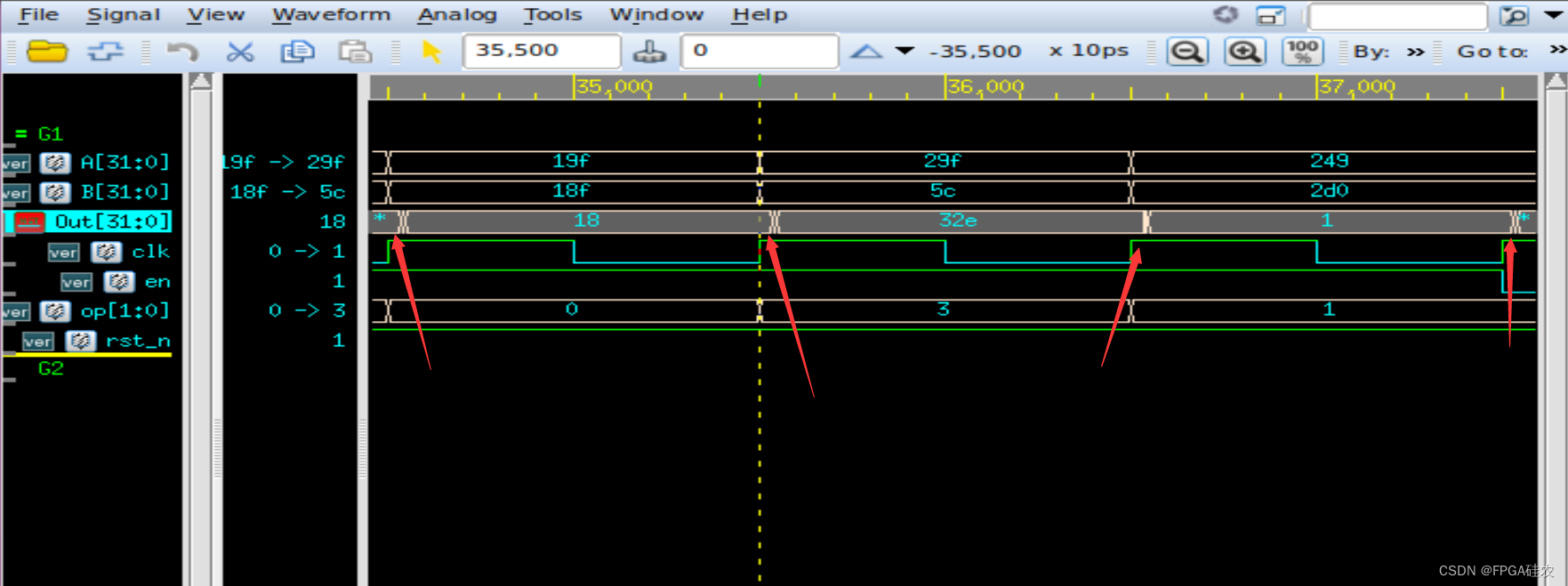

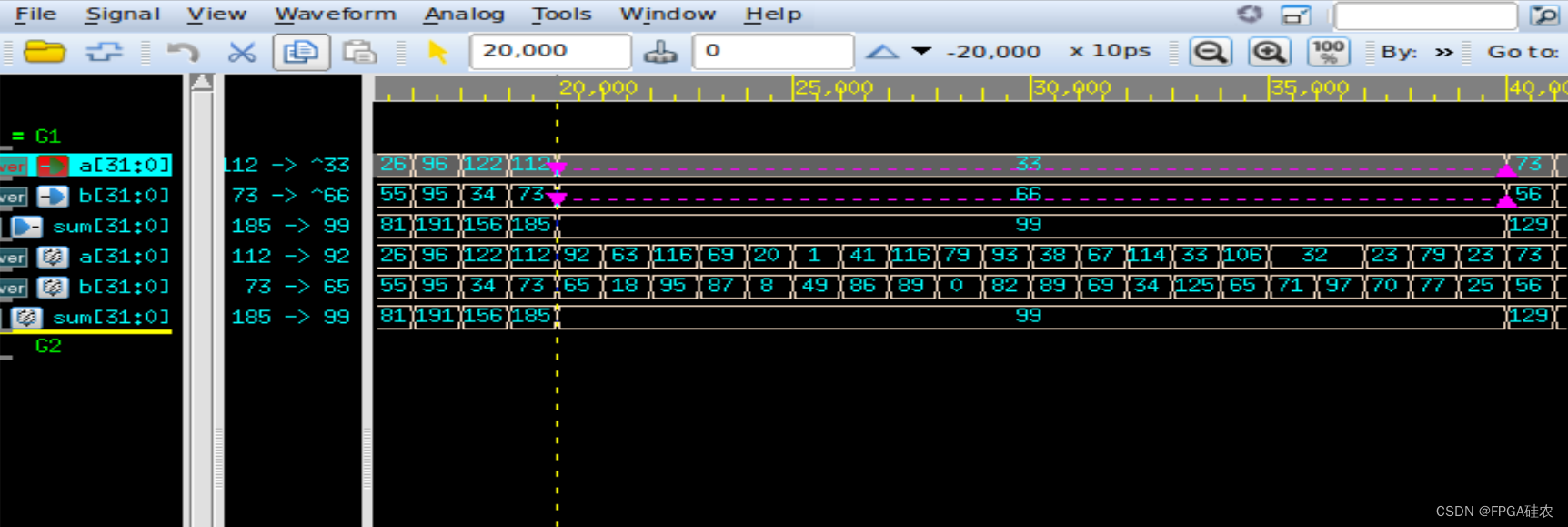

在Verilog中,将force用于variable会覆盖掉过程赋值,或者assign引导的连续(procedural assign)赋值,直到release。 下面通过一个简单的例子展示其用法: 加法器代码

module adder

(

input logic [31:0] a,

…

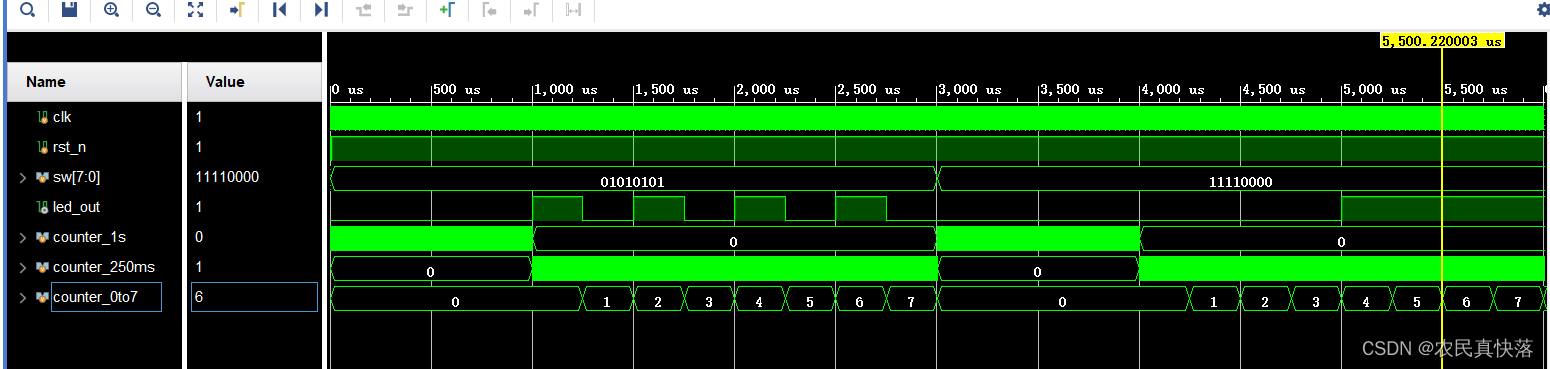

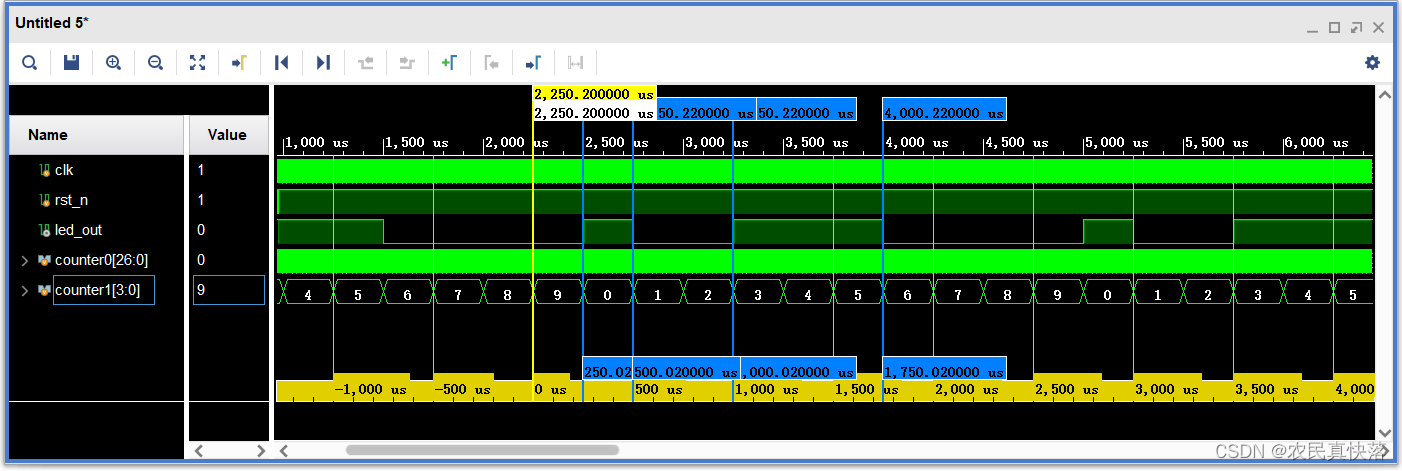

【IC设计】Verilog线性序列机点灯案例(四)(小梅哥课程)

文章目录 该系列目录:设计环境设计目标设计思路RTL及Testbench代码RTL代码Testbenchxdc约束 仿真结果 声明:案例和代码来自小梅哥课程,本人仅对知识点做做笔记,如有学习需要请支持官方正版。 该系列目录:

Verilog线性…

静态时序分析简明教程(五)]生成时钟的sdc约束方法

STA的时钟常规约束一、写在前面1.1 快速导航链接二、生成时钟2.1 标识时钟源2.2 时钟命名2.3 设定生成时钟的特性2.3.1 -edges2.3.2 -divide_by2.3.3 -invert2.3.4 -multiply_by2.3.5 时钟沿位移2.4 多个同源时钟2.5 使能组合电路路径2.6 注释时钟三、总结一、写在前面

一个数…

笔试题-2023-大疆-数字IC设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.08.07应聘岗位:数字IC设计笔试平台:赛码题目评价 难易程度:★★★★★知识覆盖:★★★☆☆超纲范围:★★★☆☆值得一刷:★★★…

笔试题-2023-乐鑫-数字IC设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.09.01应聘岗位:数字IC设计工程师笔试时长:60min笔试平台:nowcoder牛客网题目类型:单选题(2道)、不定项选择题(7题)、问答题(…

【PCIE系统学习】Gen1/2Gen3/4 symobl与OrderSet概念对比

这个专栏要干的事:学习PCIE理论知识,学会PCIE IP/VIP的使用。可以达到上手做项目,而不是空有理论

适合谁看:正在学习PCIE 设计验证,但学的过于零散。想有对比的系统的学习。 低价收费的目的:抵制胡乱传播转载现象。

版本控制:便于增加内容以及勘误 版本说明v20230829 …

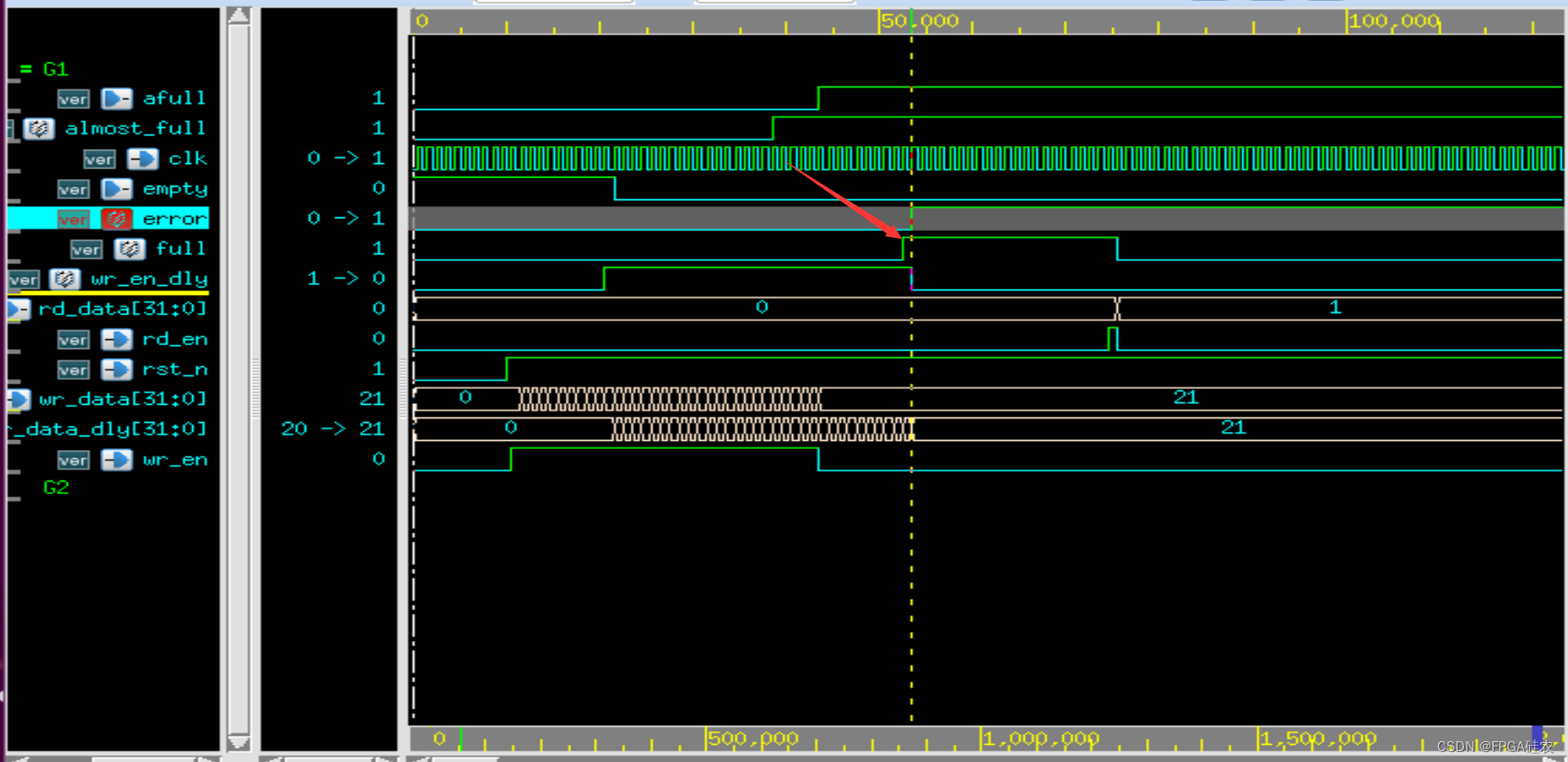

【数字IC设计/FPGA】FIFO与流控机制

流控,简单来说就是控制数据流停止发送。常见的流控机制分为带内流控和带外流控。

FIFO的流水反压机制

一般来说,每一个fifo都有一个将满阈值afull_value(almost full)。当fifo内的数据量达到或超过afull_value时,将满…

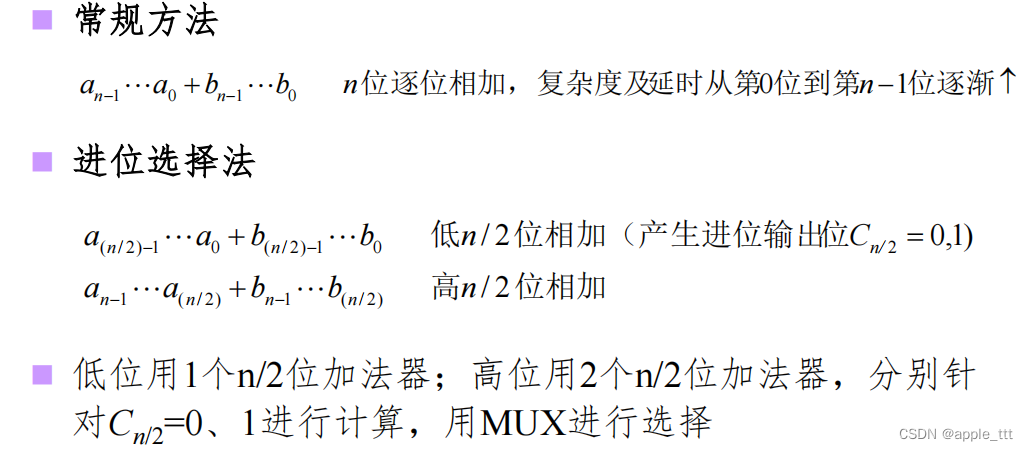

运算电路(1)——加法器

一、引言 微处理器是由一片或少数几片大规模集成电路组成的中央处理器。这些电路执行控制部件和算术逻辑部件的功能。微处理器能完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作,是微型计算机的运算控制部分。它可与存储器和外围电路芯片…

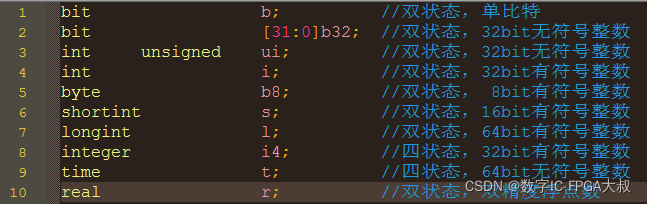

【SystemVerilog】数据类型(1)logic

相对于Verilog来说,SystemVerilog引进了一些新的数据类型,它们具有如下优点: (1)双状态数据类型:更好的性能,更低的内存消耗。 (2)队列、动态和关联数组:减少内存消耗,自带搜索和分类功能。 (3)…

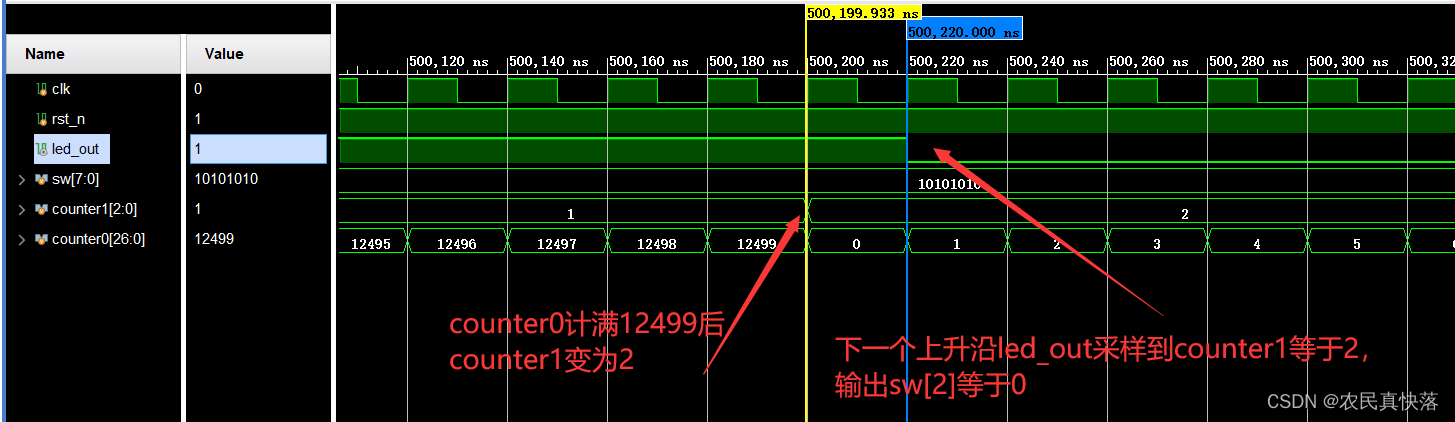

【IC设计】Verilog线性序列机点灯案例(三)(小梅哥课程)

声明:案例和代码来自小梅哥课程,本人仅对知识点做做笔记,如有学习需要请支持官方正版。 文章目录 该系列目录设计目标设计思路RTL及Testbench代码RTL代码Testbench代码 仿真结果上板视频 该系列目录

Verilog线性序列机点灯案例(一)ÿ…

笔试题-2023-荣耀-芯片设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.09.24应聘岗位:荣耀校园招聘-芯片与器件设计工程师-芯片开发笔试时长:60min笔试平台:nowcoder牛客网题目类型:单选题(40道)、不…

【IC设计】Verilog线性序列机点灯案例(二)(小梅哥课程)

文章目录 该系列目录:设计目标设计思路RTL 及 Testbench仿真结果存在的问题?改善后的代码RTL代码testbench代码 仿真结果 案例和代码来自小梅哥课程,本人仅对知识点做做笔记,如有学习需要请支持官方正版。 该系列目录:…

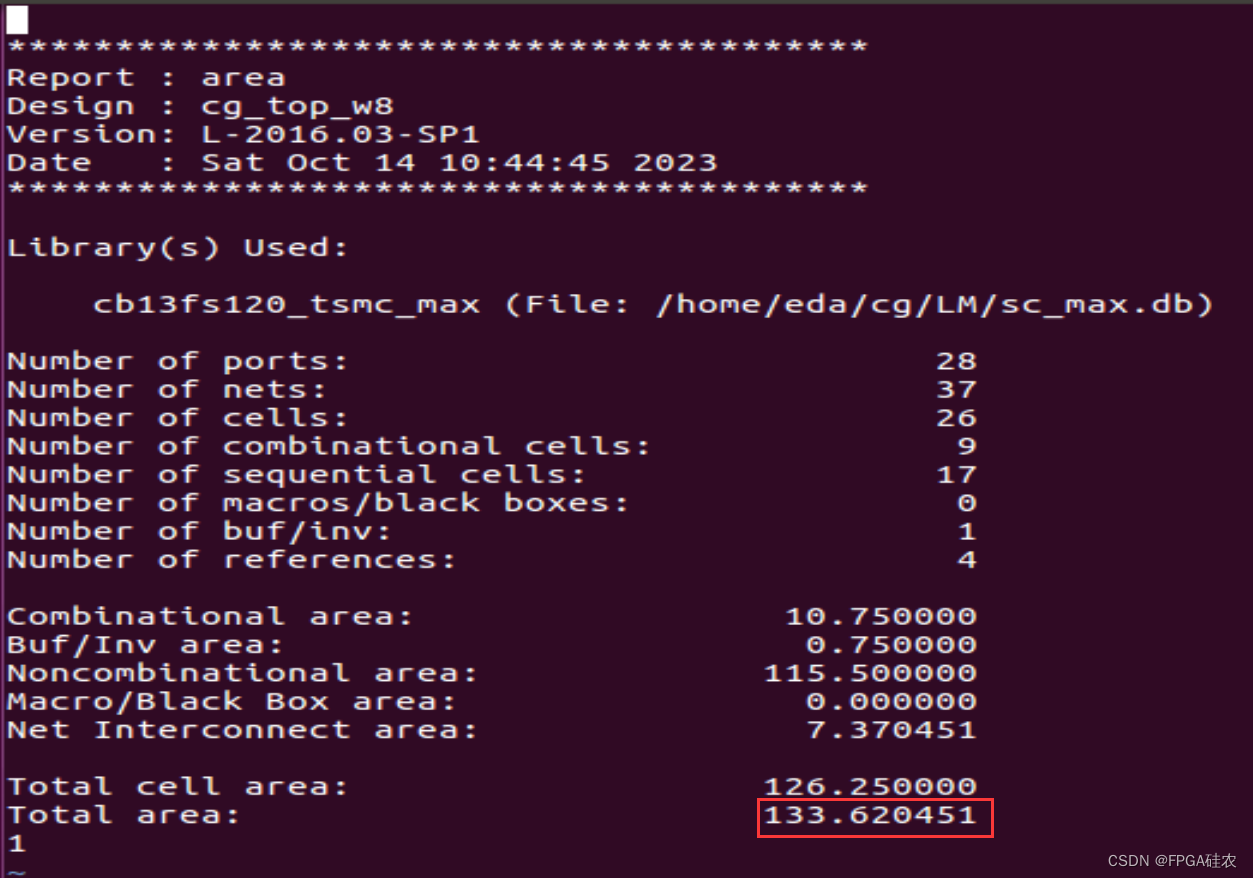

【数字IC设计】DC自动添加门控时钟

简介

数字电路的动态功耗主要是由于寄存器翻转带来的,为了降低芯片内部功耗,门控时钟的方案应运而生。作为低功耗设计的一种方法,门控时钟是指在数据无效时将寄存器的时钟关闭,以此来降低动态功耗。

在下图中,展示了…

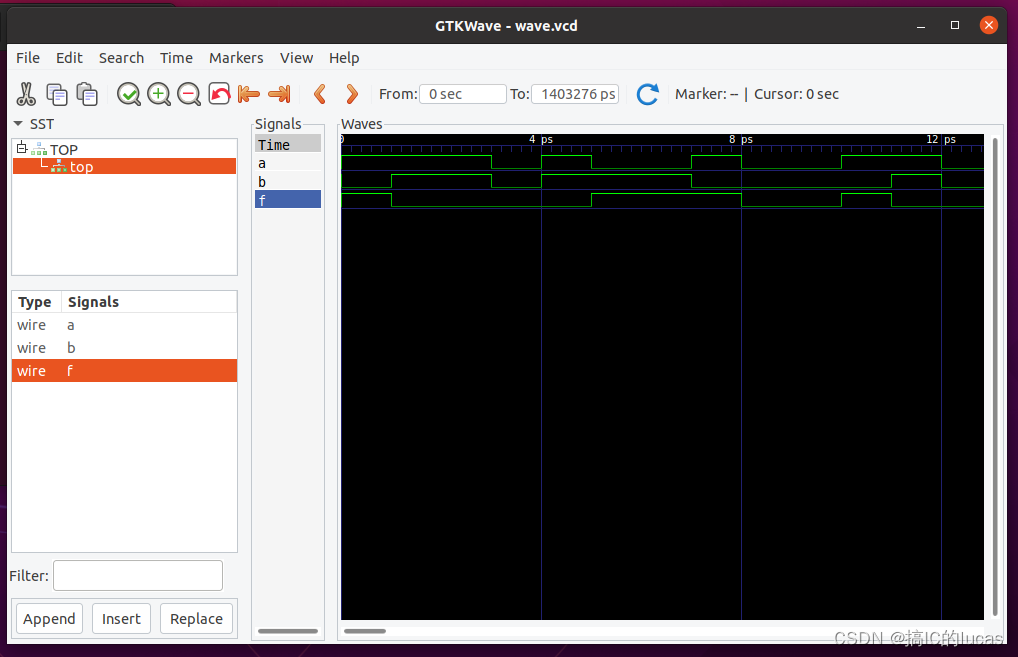

Verilator+gtkwave

一、官网介绍

1.官网:

Veripool

2.介绍:

Verilator:最快的 Verilog/SystemVerilog 模拟器 执行 lint 代码质量检查接受可合成的 Verilog 或 SystemVerilog编译成多线程 C 或 SystemC创建 XML 用于自己的工具的前端

3.What Verilator Do…

2024届数字IC设计秋招面经-鼎信

背景

985硕士,计算机科班,实验室做cpu设计和fpga算法加速,我做处理器安全方向,有项目。

投递 8.25

没有笔试,两轮面试,直接通知下周一面试,草草的准备了下。

一面 技术面 9.4

不到半小时

…

数字IC/FPGA面试笔试准备(自用待填坑)

文章目录 前言常见的IC问题数字电路基础问题Verilog & SV跨时钟域信号处理类综合与时序分析类低功耗方法STA(静态时序分析)RTL设计(包含手撕代码)总线问题AXIAPBAHB体系结构的问题RISCV的问题一些笔试选择题前言

这是实验室师兄面试过程中整理的面试和笔试题目,目前只有题…

[静态时序分析简明教程(十)]组合电路路径set_max/min_delay

静态时序分析简明教程-组合电路路径 一、写在前面1.1 快速导航链接 二、组合电路路径2.1 SDC约束2.2 举例 三、总结 一、写在前面

一个数字芯片工程师的核心竞争力是什么?不同的工程师可能给出不同的答复,有些人可能提到硬件描述语言,有些人…

Verilog学习记录

目录

一、Verilog简介

(一)Verilog 的主要特性

(二)Verilog的主要应用

(三)Verilog设计方法

二、Verilog基础语法

(一)标识符和关键字

(二)Verilog数据…

【数字IC设计】Verilog计算x/255的商和余数

问题描述

已知x是16位无符号整数,求x除以255的余数和商。尽量降低实现方式的硬件开销(包括面积和时序)

思路

由于除数255是一个常数,因此,直观上给人的感觉就是应该有相应的优化方法,即相对于除数可变的实现方式,在面积、时序方面应该有所改善。 对于该问题,本文给出…

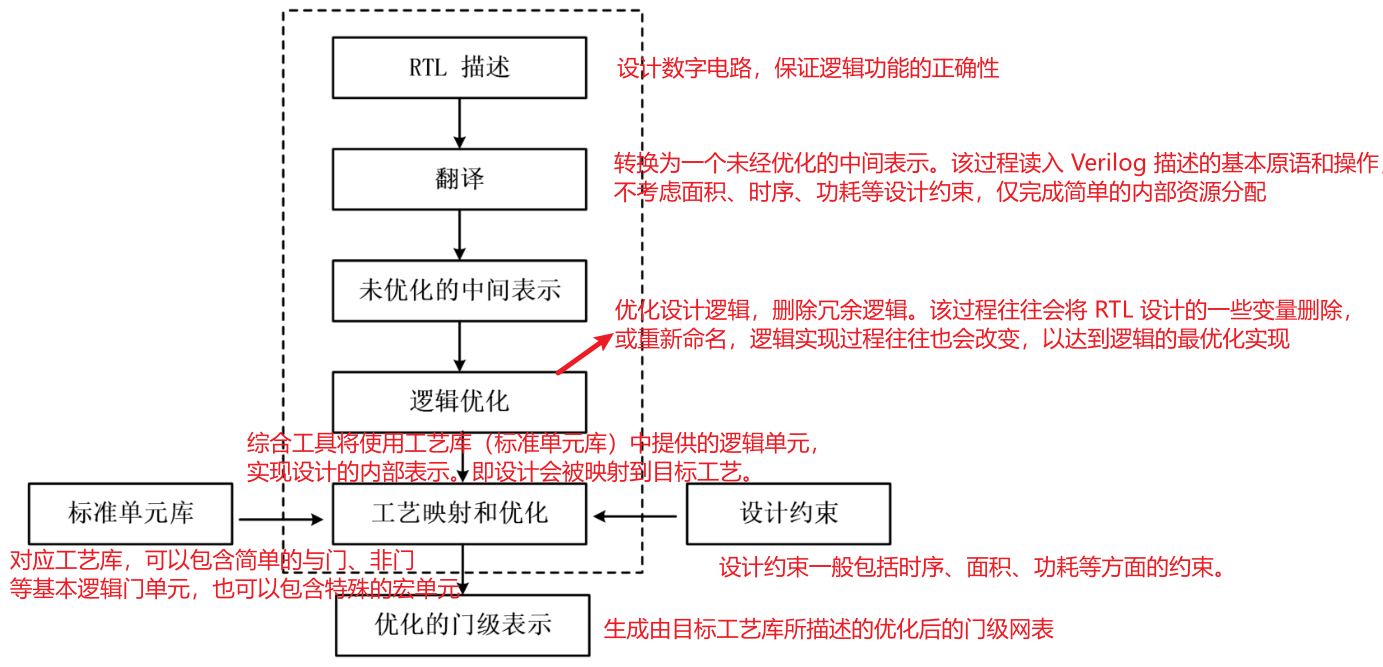

【数字IC设计】VCS门级网表仿真

本文参考自文章。 除了RTL仿真以外,在IC设计过程中还会进行门级网表的仿真。当设计代码功能仿真通过之后,我们便使用Design Compiler工具对其进行逻辑综合,将RTL代码转化为由与、或、非等门电路和触发器组成的电路,称为门级网表(n…

![静态时序分析简明教程(五)]生成时钟的sdc约束方法](https://img-blog.csdnimg.cn/121d3a9881b7403690a006d6f6eceb65.png)

![[静态时序分析简明教程(十)]组合电路路径set_max/min_delay](https://img-blog.csdnimg.cn/8b22587582384a26958c97eb94073580.png)